与主开关管 MOSFET 源极相连接的电流反馈电阻阻值

CR6850D注意事项:

1).CR6850D芯片在设计初始为了降低系统在空载或较轻负载的状态下系统整机的功率损耗,系统正常工作时CR6850D FB 端允许的最大的输出电流 IFBmax≈2.2mA,最小工作电流 IFBmin≈0.18mA;即流过光耦接收端集射极的电流 Ic 最大为 2.2mA 左右,最小为 0.18mA 左右。假设光耦的最大传输比 CTR=0.8,系统二次侧(次级) TL431 的工作电流仅由流过光耦发射端二极管的电流 IF 提供,那么通过 Ic 折算到流过光耦发射端二极管的电流 IF 最大仅为 0.74mA,这个电流将无法满足 TL431 的最小工作电流(1mA),所以在系统设计时,使用 CR6850D 设计的系统必须给次级 TL431 提供一个常态偏置电阻,使 TL431 工作在正常的状态,否则系统的负载调整率或其他性能可能会发生异常,在 12V 输出的系统中,考虑空载或轻载时系统的损耗因素,推荐使用的偏置电阻阻值为 1KΩ。

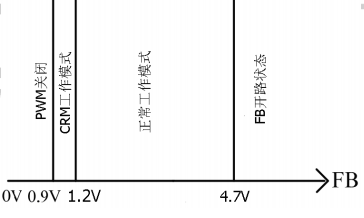

2).当 VFB=0.9~1.4V 时系统工作在 CRM 工作模式,如果系统出现可听及的异音,请先检查芯片工作频率是否工作正常,如果你确认无误,请检查系统缓冲吸收回路中的电容材质,如果使用的是普通压电陶瓷电容,那么当系统在 CRM 工作状态时电容由于发生压电效应而产生异音是很可能的。这时请更换电容的材质,如 MYLA,PEA,MEF 或 CBB 等薄膜类电容;考虑成本及电容体积大小的因素,我们推荐使用 MYLA(缇纶)电容,在保证吸收回路效果的前提下可以通过调整缓冲吸收回路中的电阻阻值来减少该电容的值有利于缩小电容体积及降低系统成本。

3).当系统工作在满载的情况下,如果系统出现可听及的异音时,请检查系统是否工作正常,如果你确认无误,请检查芯片的 FB 端的电压波形是否较平滑,如果发现较大的干扰请检查系统的 PCB layout是否合理,对于较小的干扰可通过外加滤波网络进行抑制,如图1.7.2中的RFB 及 CFB 组成的低通滤波器,这里 RFB,CFB 的取值不宜过大,比如47 Ohm,1000 PF;根据系统的实际情况,RFB 可以为 0 Ohm。RFB,CFB 的取值会影响系统的 环路稳定,一般 CFB 的取值建议要≤4700PF。

图 1.7.2 FB 低通滤波器

4)、当系统工作在输出空载,轻载或满载转空载的情况下,如果发现输出端电压在较大范围内波动时,首先确定电路设计、PCB layout 是否正确及环路是否稳定,如果确定无误,请再次检查变压器给芯片供电的辅助绕组是否能保证系统在输出空载或轻载的情况下芯片 VDD 端的电压在 10.2V(UVLO 典型值)以上,否则系统可能工作在 UVLO 临界状态。值得注意的是变压器辅助线圈在设计时需要把与 VDD 端相连的整流二极管的管压降以及限流电阻的压降考虑进去,另外还要考虑变压器层间耦合系数/强度的关系;耦合较弱时,空载时芯片 VDD 端电压值较低,容易进入 UVLO 状态,但是满载状态下 VDD 端电压上升较少;耦合过强,对提高空载时芯片 VDD 端电压稳定系统有较大的帮助,但满载状态下 VDD 端电压上升较多,容易让芯片进入OVP 状态。考虑到系统满载瞬间转空载或空载瞬间转满载时由于能量瞬变导致 VDD 端电压下冲误触发 UVLO的原因,在系统允许的输入电压范围内且系统输出为空载时建议芯片 VDD 端电压要>11.5V,特别要注意高

端输入电压如 264V/50Hz 时的情况。

6. Rsense 输入端

CR6850D 采用电流模式 PWM 控制技术,初级峰值电流通过电流检测电阻 Rsense 转化为电压反馈到 Sense端。由于在开关管导通瞬间会有脉冲峰值电流,如果此时采样电流值,会导致错误的控制。内置的前沿消隐(LEB)电路,就是为了防止这种错误的控制。在开关管导通后,经过一段前沿消隐时间(典型 300ns)才去控制电流限制比较器,可以为系统节省一个外部的 RC 网络。如果由于 Sense 端的电流反馈信号前沿噪声干扰持续时间超过芯片内置的前沿消隐(LEB)时间导致系统性能异常,可以考虑外接 R-C 网络,但建议 R-C 的取值不宜过大,否则可能会引起电流反馈信号的失真过大,导致系统启动或输出端短路时 MOSFE 漏源端电压 Vds 过高等常见的系统异常现象。推荐 R-C 网络的取值为:R≤680Ω,C≤1000PF。没有特别的需要,不建议外接 R-C 网络。正常工作时,PWM 占空比由 FB 端电压调整。

7.CR6850D可兼容LD7550BN/LD7535内置同步斜坡补偿

内置同步斜坡补偿电路增加电流检测电压的斜率,这可以改善系统闭环的稳定性,防止电压毛刺产生的次谐波振荡振荡,减小输出纹波电压。

8. Gate 端驱动:

CR6850D 内置的功率 MOSFET 通过一个专用的栅极驱动器控制。当提供给 MOSFET 驱动能力差时会导致高的开关损耗;驱动能力强,EMI 特性会变差。这就需要一个折衷的办法来平衡开关损耗和 EMI 特性,CR6850D内置的图腾驱动电路设计可以优化驱动能力。这种控制原理可以在系统设计时,容易地获得低的损耗和良好的 EMI 特性。

9、CRM 工作模式:

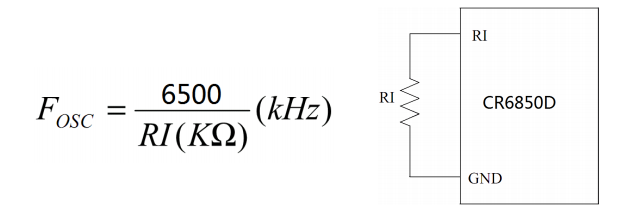

在轻载或空载时,CR6850D 进入 CRM 工作模式,工作频率降低。频率的变化由取自电压反馈环的反馈电压控制,当反馈电压低于内部门限电压时,振荡器频率线性减小到最小绿色工作频率,约 22KHz 左右(RI=100KΩ)。在此振荡频率工作时,MOSFET 的开关损耗和磁芯、电感、吸收电路等各部分的损耗均减小,从而减小了总损耗。在正常工作或重载时,PWM 频率增大到最大工作频率,约 67kHz 左右(RI=100KΩ),工作频率不受绿色工作模式的影响。

10.保护功能

1) 逐周期电流限制

在每个周期,峰值电流检测电压由比较器的比较点决定。该电流检测电压不会超过峰值电流限制电压。保证初级峰值电流不会超过设定电流值。当电流检测电压达到峰值电流限制电压时,输出功率不会增大,从而限制了最大输出功率。

2) 过压保护

当 VDD 电压超过 OVP 保护点时,说明负载上发生了过压,首先关闭输出 GATE,同时内部泄流电路开启。该状态一直保持,直到 VDD 端口电压降到 VDD_OFF后进入再次启动序列。发生过压保护后,如果 VDD端口电压超过箝位电压阀值(典型 25.5V)时,内部箝位电路将 VDD 电压箝位在 25.5V,以保护 CR6850D不被损坏,Vdd 钳位电路能承受的电流大约为 10mA(rms),如果系统由于其他原因导致 Vdd 钳位电路动作后 Vdd 端电压仍然持续上升且超过芯片的耐受能力,那么芯片就可能会被烧毁。

3)、过功率保护(OLP):

芯片 SENSE 端通过监控系统初级流过主开关管的电流信号活动,芯片能检测到系统过流或过功率的状况。当系统输出发生过功率现象时,如果 SENSE 端的电压 VTH_OC 超过 0.75V(典型值)时,Gate 端输出脉宽将会被限制输出,这时系统处于恒功率输出状态 Po=Vo*Io,即如果增加输出负载电流,那么系统输出电压相应会下降,芯片将使系统进入过功率保护(OLP)状态,Gate 会立即关闭输出,芯片 VDD 上的端口电压也随之被拉低进入到 UVLO_ON,然后芯片重新启动,当故障依然存在时系统将重复上述现象(即打咯现象)。当系统进入过功率保护状态时,系统损耗的平均功率非常低。

4)、欠压保护(UVLO):

CR6850D 都内置有欠压保护电路(UVLO),当 VDD 端电压小于 10.2(Vmax)时(考虑温度的影响建议设计参考值为 11.5V),芯片就会进入欠压保护状态,这时 Gate 停止输出 PWM。设计中需要检查交流输入全电压范围内,当输出负载瞬间由满载转为空载时芯片的 Vdd 端电压是否受影响而误触发 UVLO,即 Vdd端电压瞬时低于 10.2V(考虑温度的影响建议设计参考值为 11.5V)否则这样很容易造成空载输出电压会不稳跳动的现象。

资料太多,未完。。。

![]()

![]()