ChipLink芯联CL1830具有出色ESD保护的高压CMOS工艺

概述

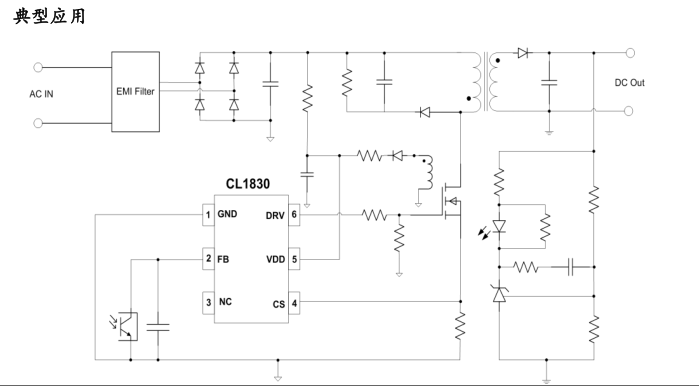

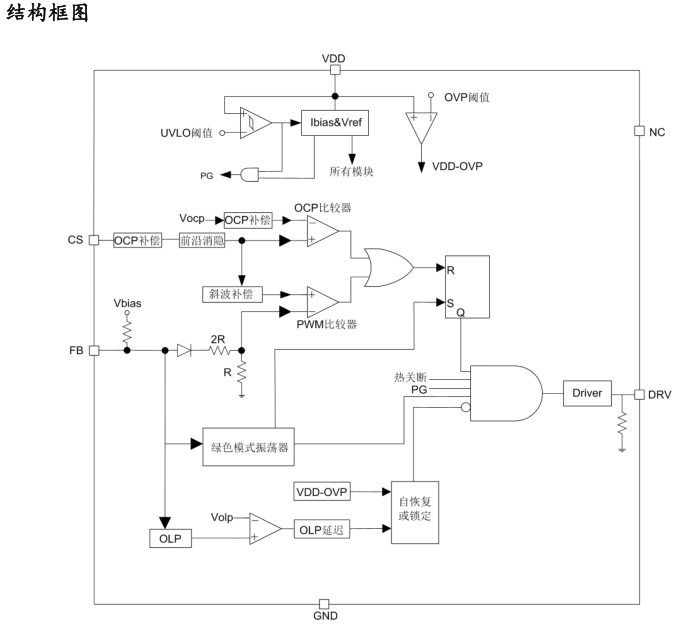

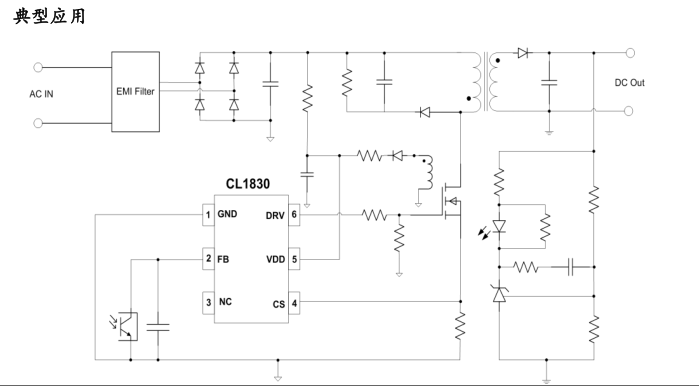

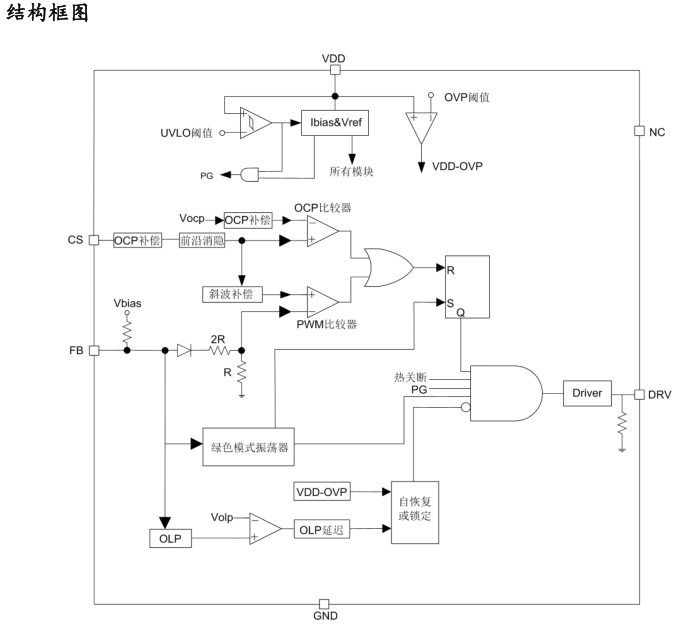

CL1830 是一款更高集成度的 PWM 反激控制器。它提供了几个功能来提高效率,轻载时,专有的绿色模式功能提

供了逐渐降频的模式。空载时,它还内置突发模式和几个参数,以完全关闭 PWM 输出,最大限度地减少外部功率管

的开关损耗。CL1830 还内置了电流检测和反馈回路的前沿消隐(LEB),以屏蔽输入信号的尖峰噪声。内置的斜坡补

偿使系统在通用输入电压范围内提供稳定的功率限制。锯齿波频率功能用于 EMI 改进解决方案。CL1830 还提供 OLP

(过负载保护),VDD OVP(过压保护)等各种保护功能,以防止电路在异常状态下损坏。

特性

◆具有出色 ESD 保护的高压 CMOS 工艺

◆软启动

◆超低启动电流

◆电流模式控制

◆内置斜波补偿

◆CS引脚上的LEB(前沿消隐)

◆非可听噪音绿色模式控制

◆欠压锁定(UVLO)

◆VDD OVP(过压保护)

◆过载保护功能(OLP)

◆光电耦合器短路保护

◆反馈开路保护

◆高抗扰度

◆符合RoHS和无卤素

应用范围

◆AC / DC适配器和电池充电器

◆ATX待机电源

◆开放式开关电源和CD(R)

◆机顶盒(STB)替代384X

保护选项

◆频率:65KHz

◆VDD OVP:打嗝

◆OLP:打嗝,65ms后保护

◆CS开路:打嗝

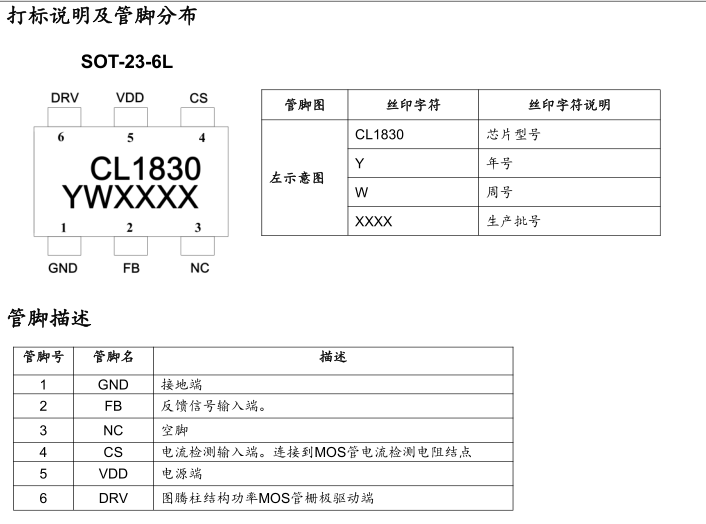

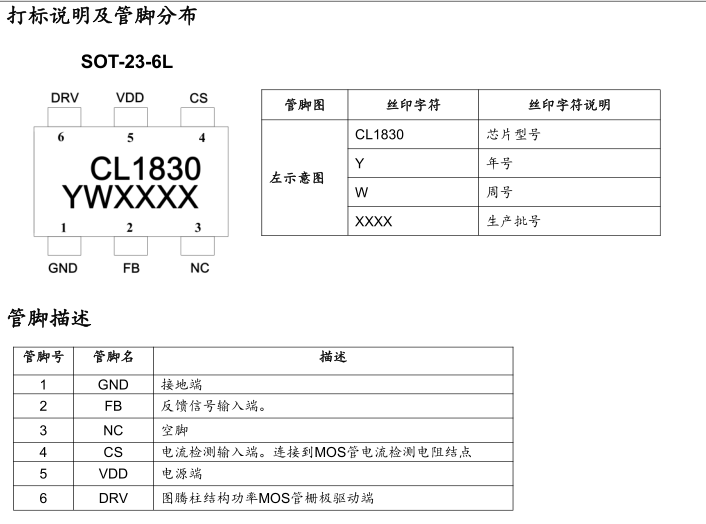

CL1830 采用 SOT-23-6L 封装

使用说明

CL1830 是一款高集成度的 PWM 反激控制器,它提供了几个功能来提高效率、EMI 改进方案,并内置完整的保护

功能。同时,芯片高度集成化以减少外部元件数量和尺寸,其主要功能描述如下:

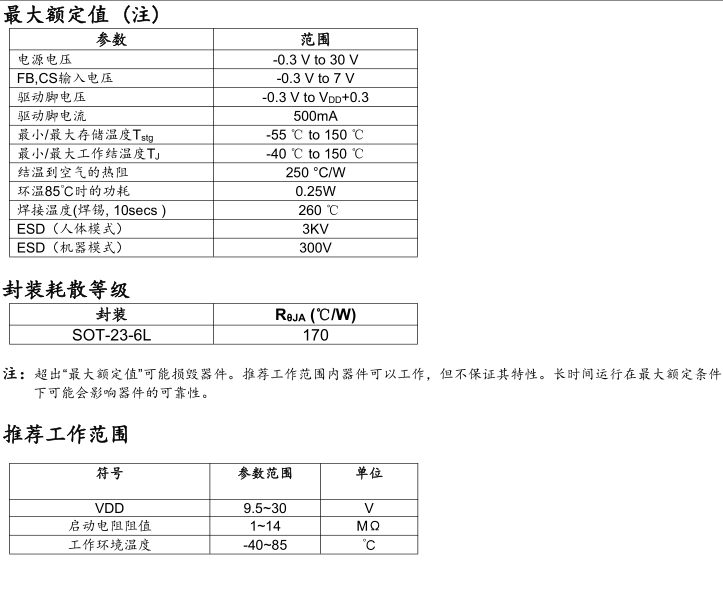

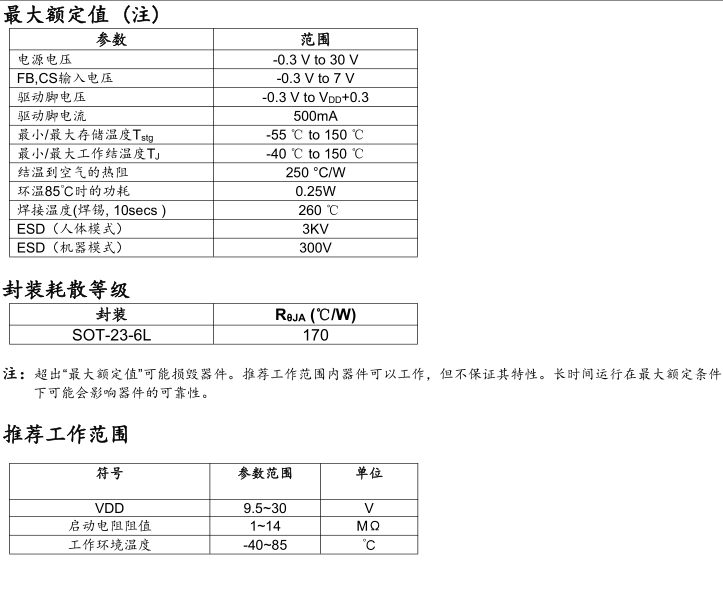

●Pin5 VDD 脚

启动期间,VDD值低于UVLO阈值,因此芯片不工作,此时,电流通过启动电阻给电容充电以抬高VDD,当VDD

电压上升到芯片退出UVLO模式后,芯片开始正常工作,输出栅极信号,变压器的辅助绕组这时给芯片提供工作电流。

较低的启动电流(不大于于6.5uA)和工作电流以及相差有12.5V之大的VDD-on和VDD-off阈值之差,意味着采用较大的

启动电阻和较小的启动电容。启动电容要能够保证满载启动和空载运行时VDD不跌落重启,启动电阻越大此电阻的消

耗越小,代表着更小的待机损耗,但启动时间相对应的就越长。因此启动电阻的选择是需要配合启动电容,折中慎重

选取的。

当VDD电容遇到正常运行不能维持的问题时(尤其在低温条件下易出现此现象),可使用二级启动,如下图,增

加CAP2以助维持正常工作。

未完。。。

由于资料过多,未上传完毕,如需更详细资料,请找客服索要!!!

![]()

![]()